丁香五月天

丁香五月天

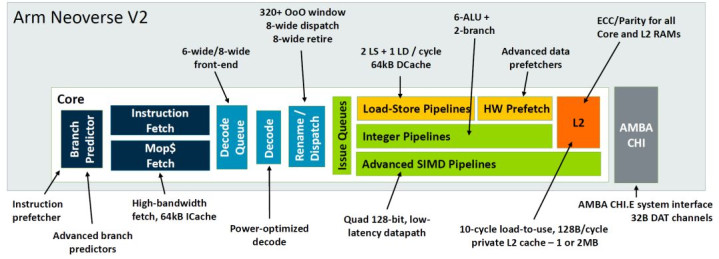

ARM V2的微架构是ARM科罚器的基础,它包括了提醒集、寄存器、适度单位等。这篇著述主要分析了ARM V2的一些微架构内容。如若您需要更顾惜的信息,不错参考这篇著述。

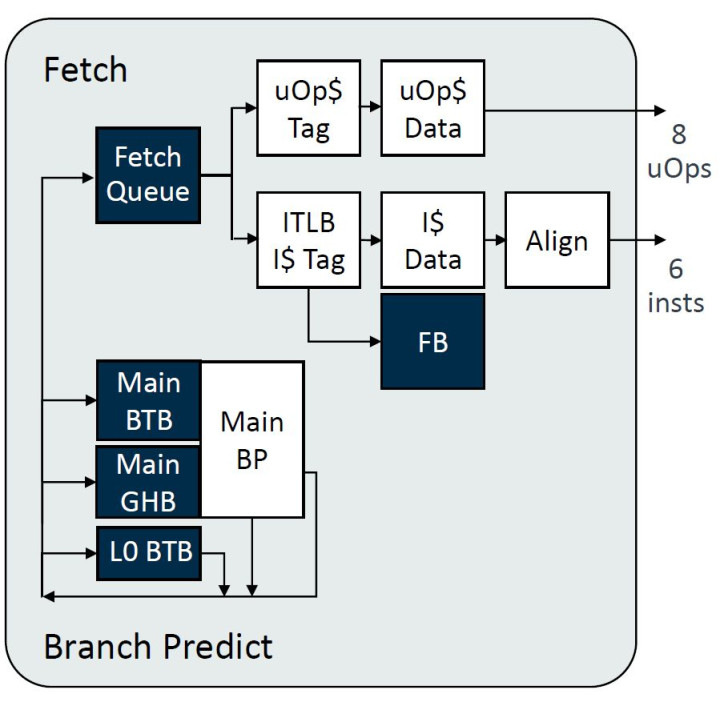

IFU

著述内容过程优化如下:1、Cycle意想两个分支的特质,在奇迹器系列N2/V2中终局难度较大。复杂度高,需均衡多种成分。

2、终局uOp Cache,这一采取在RISC提醒连归拢不常见。尽管N2/V2系列才刚终局此特质,但实质迁移端早在A77就也曾脱手剿袭这个微架构。相干词,本年发布的V3/N3却烧毁了uOp Cache想象。这可能是出于对功耗的推敲,以及优化ICache和其他IFU方面的特质所带来的收益更为显耀。相较于uOp Cache,殉国面积和功耗以取得收益的作念法似乎更为聪敏,因此N3系列采取了烧毁uOp Cache。

3、新增TAGE意想器及扩大BTB容量,属于老例升级。参数化更正为主,细节算法优化尚不解确。

4、针对曲折提醒,咱们想象了独处的意想器。相干词,由于历史原因,N和V系列实质上是从A系列演变而来的。在经典的A76微架构中,一脱手迁移端和奇迹器端的分辨并不显然,因此之前的曲折意想器与迁移端同样,都是搀和使用的。

跟着时分的推移,奇迹器端曲折提醒的比例逐步加多,而迁移端的一些微架构在细目为曲折提醒后,再查找非独处IBTB想象有蓄意(以省俭面积和功耗)可能不再适用于奇迹器端。即使进行解耦想象,也难以满盈搁置曲折提醒意想带来的延伸问题。

6、取指队伍也从原本的16entry升级到现时的32entry。

小二先生 调教

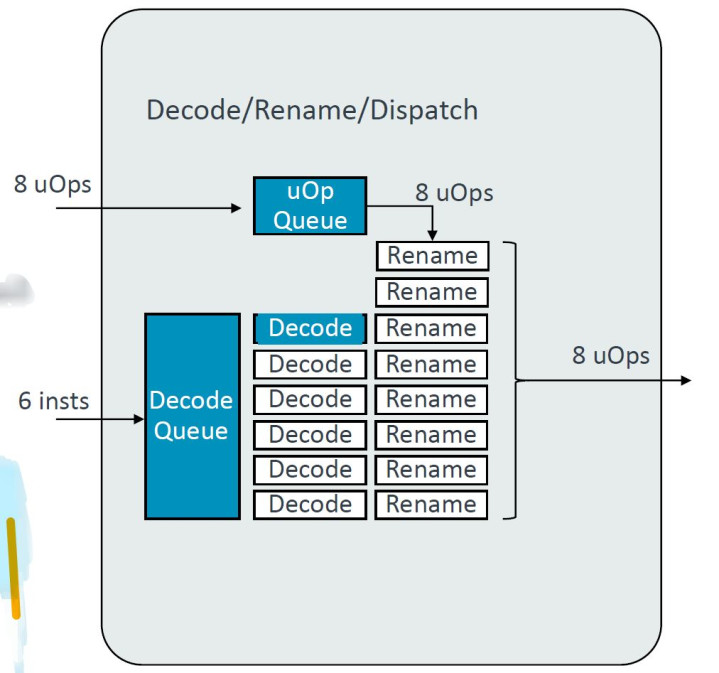

Decode/Rename/Dispatch

Decode/Rename/Dispatch细节已优化,宽度提高至6,借助uOp Cache终局低延伸发出8 uOps。Decode Queue从16增至32,新增Rename Checkpoint及优化Rename Rebuild,提高后果。

Issue/Execute

"新增了2个单周期ALUs,膨胀了Issue Queues,SX/MX从20增至22entries,VX从20加多至28entries等。"

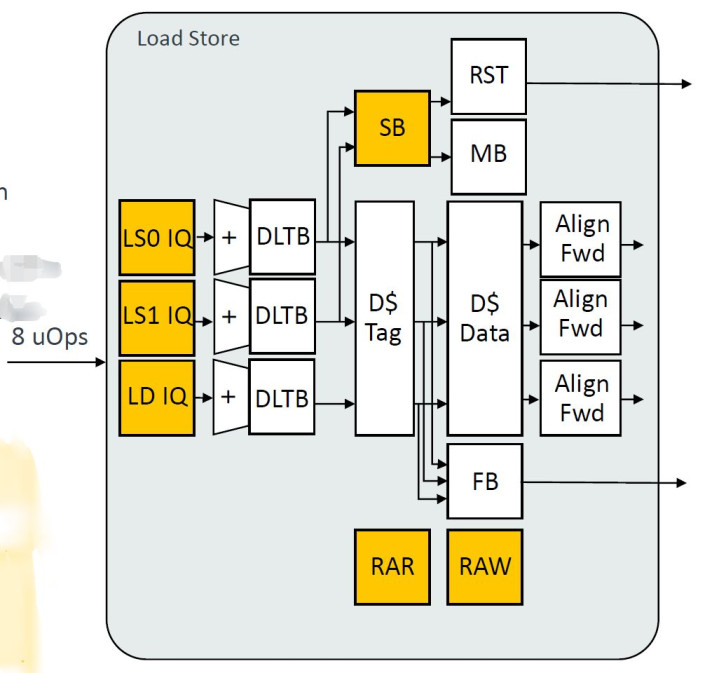

LSU

1、加多DTLB数目至48entry。

2、DCache将PLRU替换算法改为RRIP,ARM常用的替换算法,NRU/PLRU/RRIP,L1 Cache使用PLRU更多,更爱重L1 Cache的时期会殉国更多资源在替换算法上。现时论文常讲的更“细粒度”的替换算法,在实质工程中见的更时时了。举例启动化分辨历史,将数据概况提醒视作不等价等。

节略讲,有一种不雅点是不一皆强调射中率,更强更正体的性能,举个节略的例子,有些数据不射中,对其miss系统亏空的代价更高,即使依据时时走访原则“它”应该被踢掉,但由于“它”地位更高,是以不将“它”替换掉。

概况有不雅点,识别数据自己的特质以及走访频率等情况详细去考量替换问题,这无疑会耗费更多的资源,关于路数更多的L2可能使用雷同“细粒度”的替换算法收益更高。但现时ARM L1 Cache也脱手安靖使用相对复杂的替换算法。其它即是一些老例的参数级别的升级,举例2LS,1LD,一些buffer深度给出了升级。

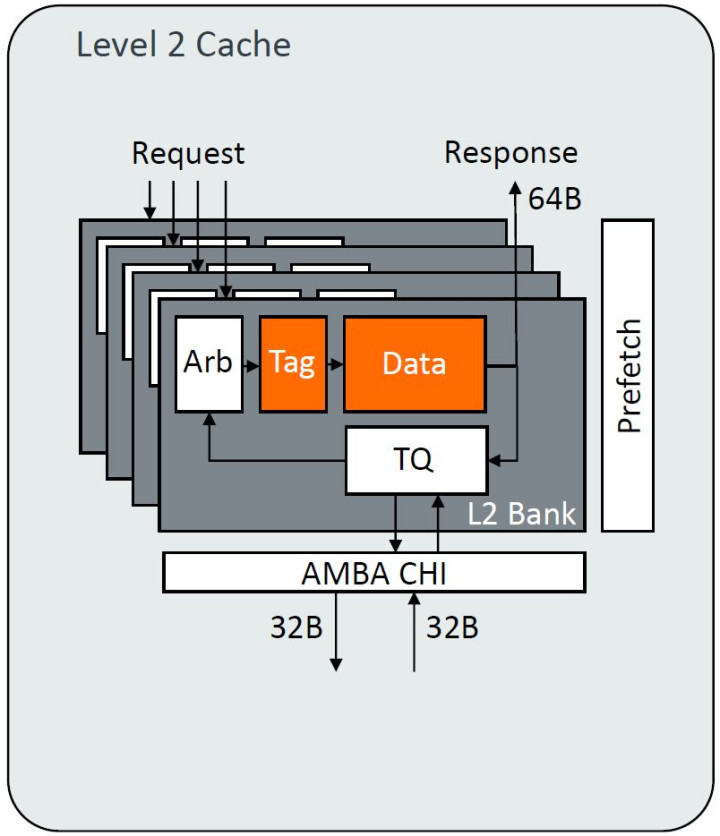

L2

8路鸠合,2MB和1MB延伸保持一致(与前版块比较)。新算法剿袭6-state RRIP。单个bank每2个时钟周期读写64B,共4个bank。

归来

arm的微架构给我的嗅觉是细节终点多,好多眇小的特质都会捏取去优化,这是国内好多公司不具备的,海外一线的CPU公司,微架构标的的优化每年提高都放缓了,更多的是面向特定场景的优化,反而是工艺的提高以及SoC系统级微架构的提高对芯片系统的影响更大了。

诚然国内对CPU微架构的想象依然相对逾期一些,即使在“参数上”追上了海外水平,何况抛开一些生态问题,实质“面积”“功耗”以及老例情况下的性能依旧有不少的提高空间。

-对此丁香五月天,您有什么概念见地?-